CS-391 – Car in a Box March 27, 2006

### **Hardware Review**

A **bypass capacitor** placed very close to the microcontroller provides a burst of current to bring the signal high very fast as the processor needs it.

The **reset pin** is connected to an RC circuit that keeps the voltage low for just long enough as the system starts up to meet the requirements specified by Motorola in the reference manual.

| MODB        | MODA            |                                      |

|-------------|-----------------|--------------------------------------|

| 0           | 0               | Special single-chip                  |

| 0           | 1               | Special expanded mode (special test) |

| 1           | 0               | Normal single-chip                   |

| 1           | 1               | Normal expanded memory mode          |

| 0 = special | 0 = single chip |                                      |

| 1 = normal  | 1 = expanded    |                                      |

The **special test mode** gives privileged access to registers to which access is normally blocked, such as HPIO.

The intent of the **pull up resistor** is to protect the power supply. If it weren't there and we pushed the button, ground and the power supply would be connected and cause a short. The pull-up resistor provides a path through which current can flow.

One of the first things the small OS program (provided by JBug or WinBug) does is switch the processor into expanded mode. Otherwise, there would be very limited 512-bytes of on chip memory.

# **Expanded Mode**

Expanded mode uses up Ports B and C

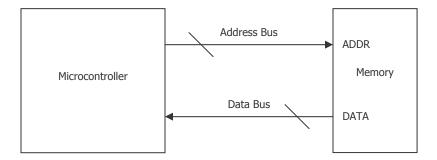

#### **Data Bus**

The collection of wires that is being used to move voltage to the address location.

# **Memory Interfacing**

The crystal frequency is four times as fast as that of the system clock's frequency, E.

CS-391 – Car in a Box March 27, 2006

The HC11 requires that memory be synchronous. It must respond within one period of the system clock, or within 500 microseconds on our processors.

RW is a signal that is produced by the microcontroller. It is the controller stating "I am reading from memory." Or, "I am writing to memory." It is a controller signal, not a memory signal. When it is low, it is a memory write signal. When it is high, it is a memory read signal.

### Address strobe

The processor tells the memory chip, "I am announcing the memory address. Grab it."

Strobe means to command it to do something. Thus, address strobe is the command to grab this address.

It is a pulse, like a strobe light.

The tri-state condition is critical to sharing multiple devices on a single signal wire.

# Similarities between Reading & Writing Memory

Both drive a set of signals known as the address bus, data bus, and the control bus.

## In our example:

The control signals are E, RW, and AS The address signals are a15:a0. The data signals are d7: d0.

# **Memory Interfacing**

The addressing phase occurs when the E clock is low.

The data phase occurs when the E clock is high.

The fact that the HC11 takes away the lower address byte means that it has to be stored somewhere.